Overview

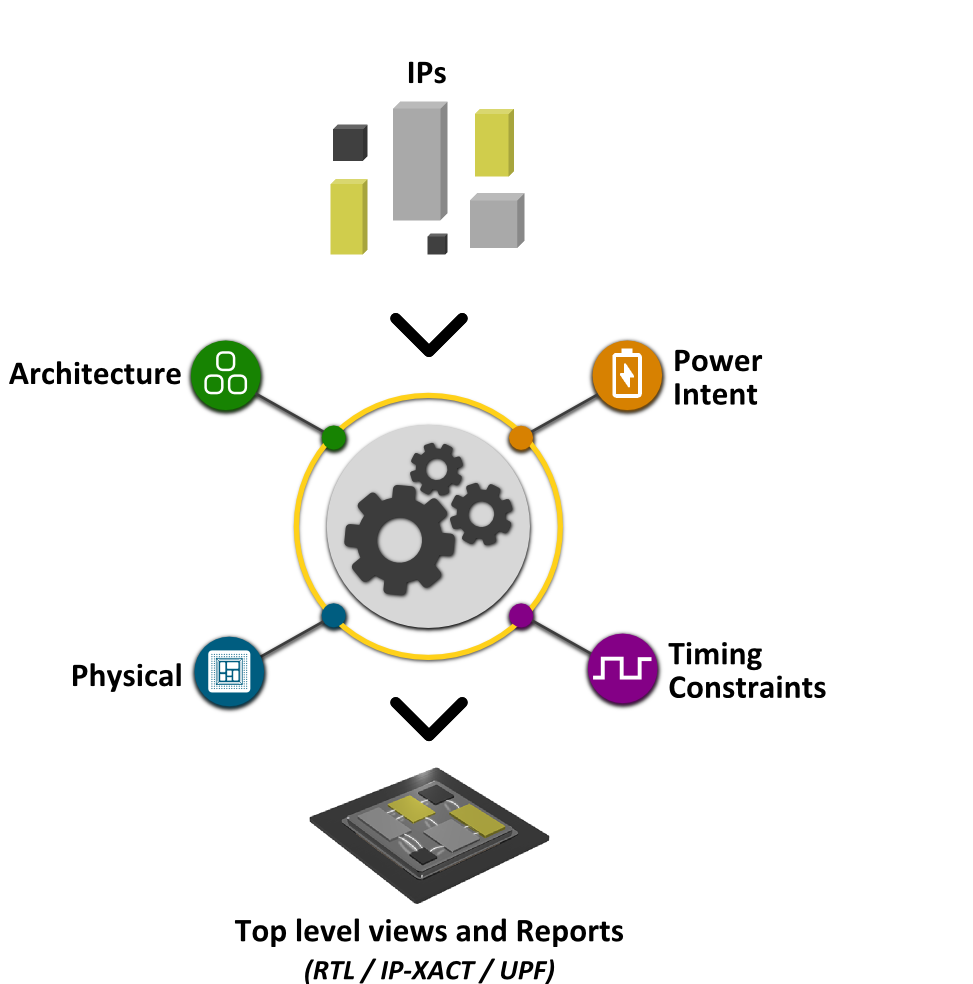

Defacto’s SoC Compiler is a complete SoC integration platform multidimensional and pre-synthesis with a high level of automation taking in consideration all design information, including RTL, IP-XACT, timing constraints, power, physical, and test.

Before logic synthesis, SoC Compiler enables full implementation capabilities towards IP and connectivity insertion, design editing, views generation with real-time monitoring of the integration progress.

This enables SoC creation in minutes and maximizes design reuse from existing projects. In particular, Arm IPs are fully supported in the tools and SoC Compiler has been widely used to build the most complex Arm-based subsystems.

SoC Compiler is certified ISO26262 and can be fully used in FuSa design flows.

High Level Benefits

- Assist reaching best possible PPA combination within a tight schedule

- Bring more automation into SoC Integration flow before logic synthesis

- Augment existing front-end SoC assembly and integration flows towards a more unified integration process by considering several design collaterals RTL, IP-XACT, SDC, UPF, LEF/DEF, etc.

- Get up to 90% and higher of design reuse including RTL and design collaterals

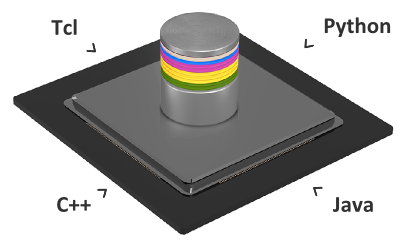

- Easily migrate internal scripts and tools with the support of rich APIs high Tcl and Python and low level: Python, C++.

- Reduce drastically TAT and engineering effort by minimizing design iterations

- Enable non-experts to perform design engineering tasks (power, architecture, testing, etc.) through simple APIs

- Enables SoC creation even if design blocks and views are missing

High Level Key Features

- Multi-format IP cores insertion including Verilog, System Verilog, VHDL, IP-XACT 2009, IP-XACT 2014, even mixed and uncompleted.

- Automated and hierarchical connectivity insertion including System Verilog and IP-XACT interfaces

- Full interoperability with Arm IPs and configuration tools

- Real-time monitoring of the SoC integration progress

- Physically, Power and Timing-aware integration process at RTL

- Design Reuse and Packaging of IP cores and subsystems.

Typical Applications

RTL Integration

Overview

SoC Compiler provides unique capabilities to build a complete SoC at RTL with all the mechanisms to edit the design, stitch IPs together, and generally to make the assembly of a complete SoC, delivering a correct-by-construction RTL and the associated views such as IP-XACT, SDC and UPF, ready for synthesis.

Key Features

- Full language support

- Verilog, SystemVerilog, VHDL or a mix

- Any input is supported (and optional): IP-XACT, UPF, SDC, LEF/DEF, .lib

- No need to package IP before integration

- Full support of Arm IPs

- Top level creation from scratch or using existing top RTL

- IP Integration with full parameterization of instances

- Automatic connectivity insertion

- Automatic core and memory wrapping

- “on the fly” design refactoring

- Generation of different integration configurations based on Power, Physical, Timing information

- Generation of the Top level RTL view

- Generation of the design views as well: IP-XACT, UPF, SDC

System Integration

Overview

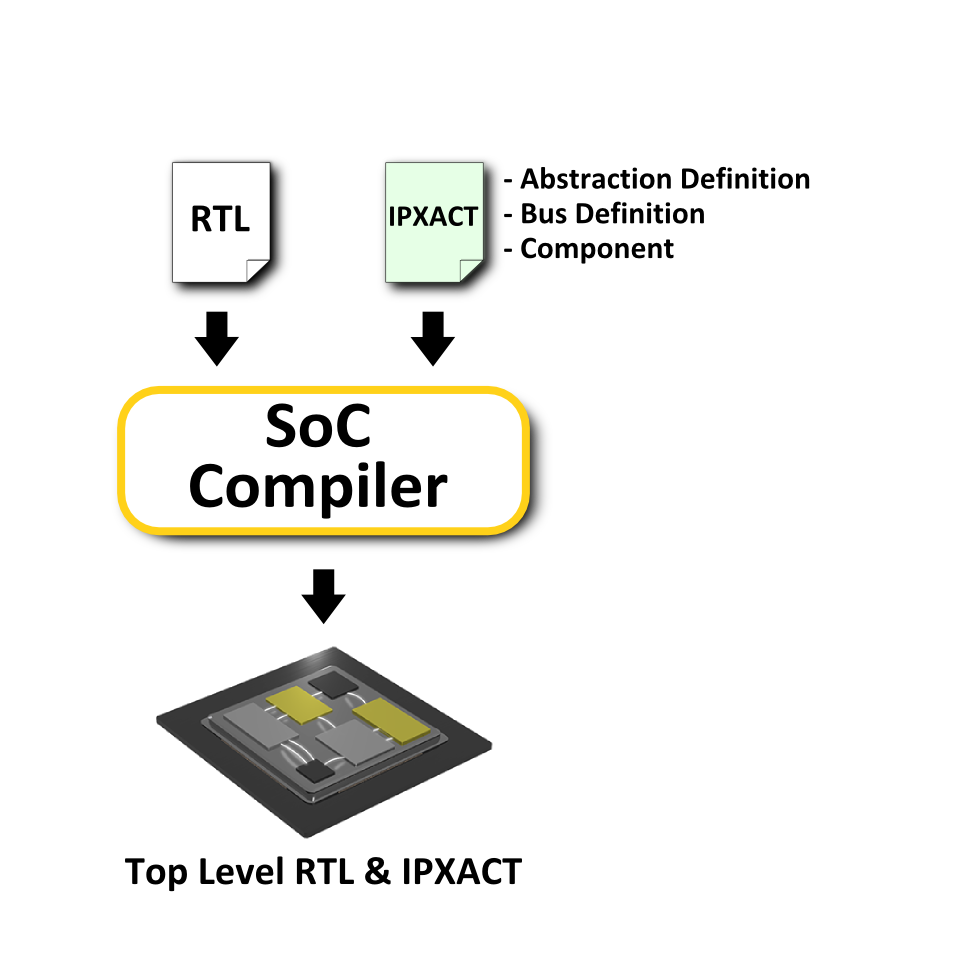

SoC Compiler enables the SoC design assembly process with full support of IP-XACT standard in full compliance with RTL files. Several automated design “extraction, packaging and reuse” capabilities are provided. Extraction of the system memory map is also part of the SoC Compiler capabilities. Defacto is part of the Accellera committee for the definition of IP-XACT standard and an active member of the IP-XACT 2021 version

Key Features

- Full language support

- IP-XACT 2009 / IP-XACT 2014

- Vendors extension

- IP-XACT component and design creation from scratch

- IP-XACT can be read instead or in parallel with RTL

- Automatic connectivity insertion using standard busses, ad-hoc, etc.

- View translation between IP-XACT & RTL

- RTL generation from IP-XACT

- IP-XACT generation from RTL

- Coherency checks between RTL and IP-XACT

- Design attributes unification

- Generation of IP-XACT top level view

- Extract System Memory Map

- Trace bus interconnects from initiator to targets

- Collect address data information at each connection node

- Resolve addresses to report the system easily

- Generate documentation (HTML, RDL, .h, etc.)

This email address is being protected from spambots. You need JavaScript enabled to view it.

Power Integration

Overview

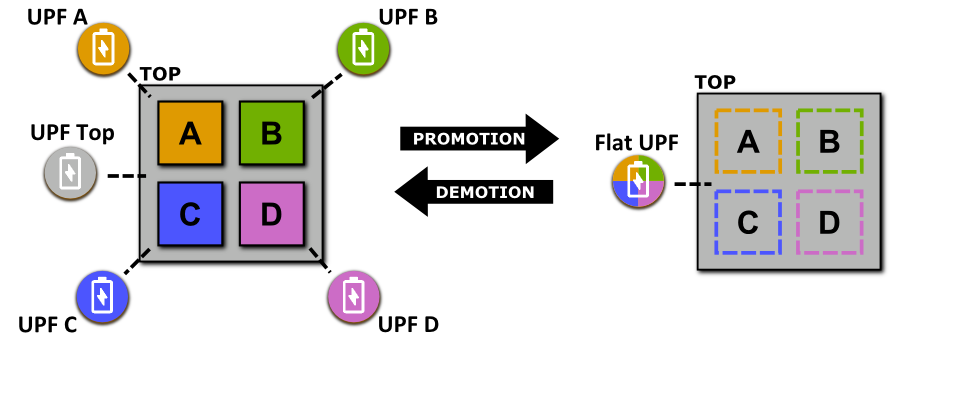

During the SoC integration process, SoC Compiler automates the management of power intent through an automated generation, update, promotion and demotion of UPF files. Power Intent Static Checks and UPF-vs-RTL coherency checks are also provided as part of the power integration process.

Key Features

- Full language support: UPF 1.0 / 2.0 / 2.1 / 3.0 / 3.1

- Complete power intent checks including UPF linting and coherency checking with RTL and Liberty files.

- UPF Promotion to help promoting existing UPF files and generate a top level UPF file

- UPF Demotion to help extracting UPF files from hierarchical blocs & subsystems

- UPF Update as soon as a design change occurs

- UPF Generation from scratch

- From Excel (XLS) or custom template

- Ability to update XLS file post UPF modifications

Customer statement at DAC 2022: “This solution has proven its reliability and optimized performance. With simple API interactions, overall scripting process to integrate the features into our custom flow is smooth.”

This email address is being protected from spambots. You need JavaScript enabled to view it.

Clock Integration

Overview

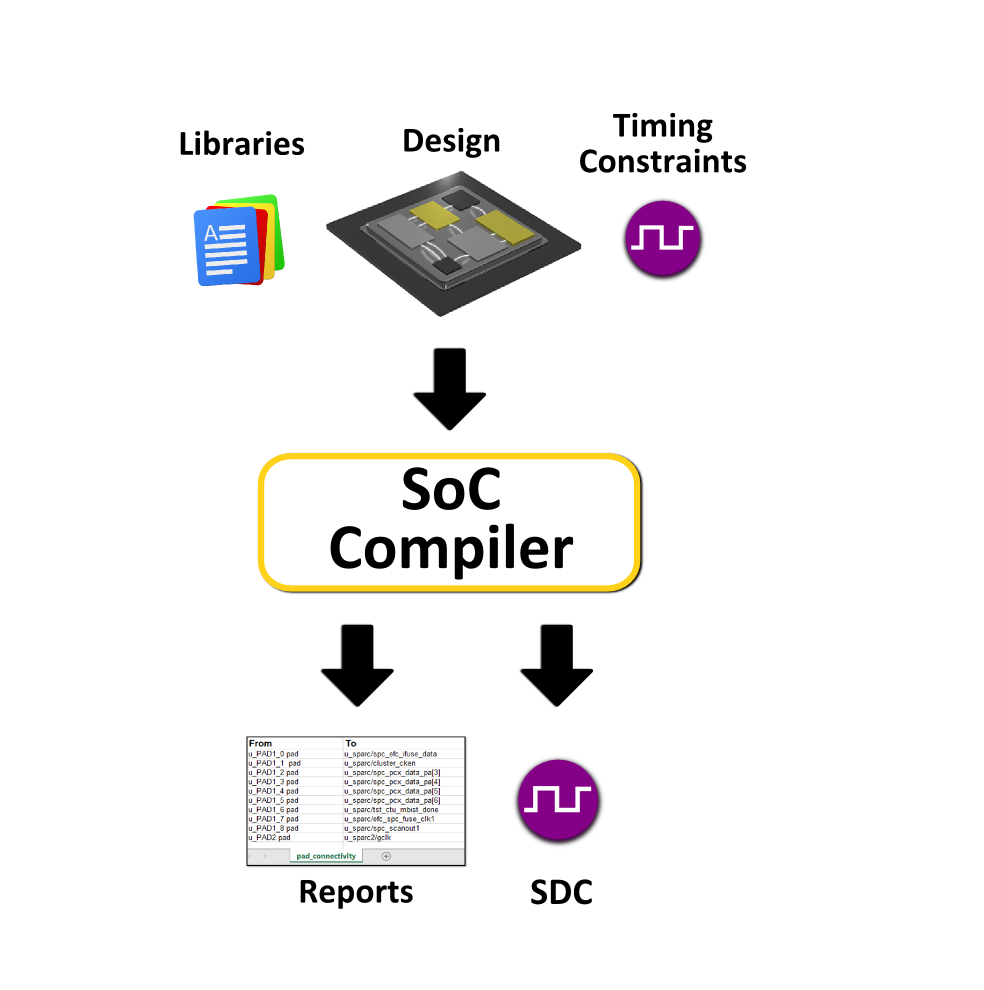

SoC Compiler enables several clock management capabilities as part of the SoC integration process. Clock-tree exploration, checking and generation of timing constraints are provided, including SDC management pre-synthesis.

Key Features

- Clock tree exploration

- Identification of clock sources and potential pin constraints

- Dedicated DRCs for master / generated clock path checks

- RTL vs. SDC Coherency Checks

- GUI based exploration and debug environment

- SDC update files whenever a design is modified

- SDC generation from scratch

- SDC management and update files whenever a design is modified

This email address is being protected from spambots. You need JavaScript enabled to view it.

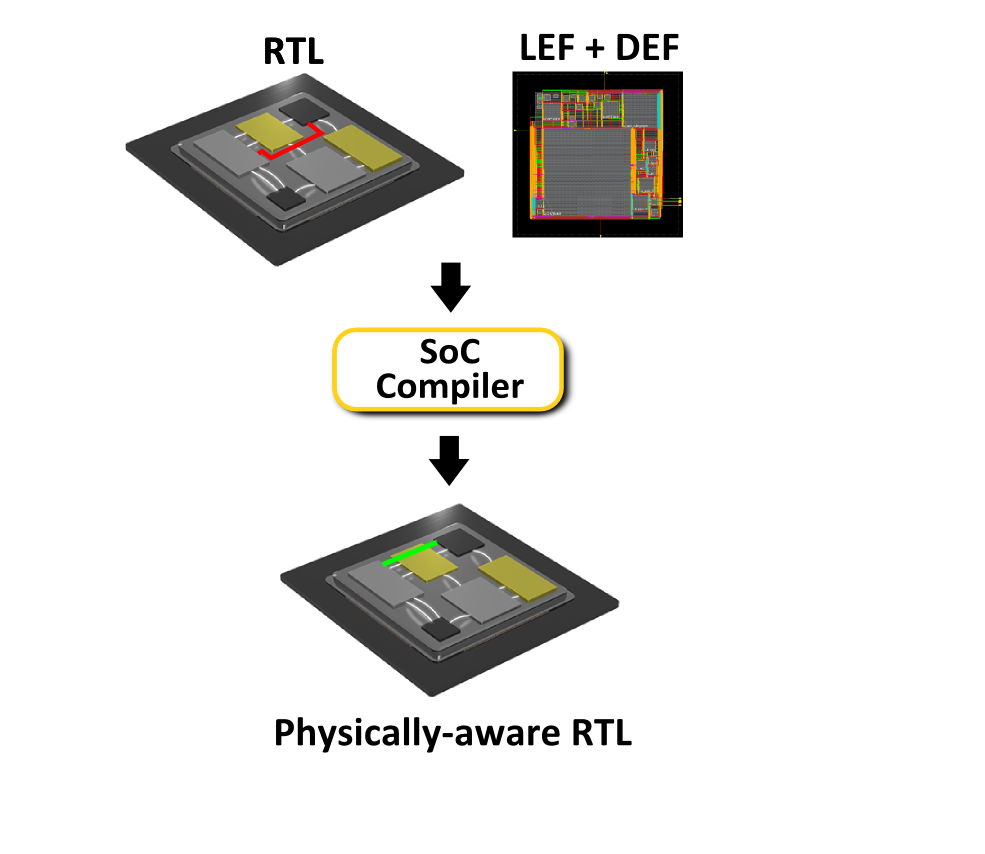

Physically-aware Integration

Overview

SoC Compiler enables the consideration of physical design information which are contained in LEF/DEF file to let the SoC integration process lead to better PPA results, in particular, reducing overall chip size area. Optimizing design for back-end will reduce the P&R effort by avoiding many iterations between Back-end and Front-end.

Key Features

- Data extraction from LEF/DEF

- Parsing checks (Syntax, Semantic, etc.)

- Data extraction from Design

- Automated LEF/DEF-based design restructuring

- Automatic Feedthrough insertion based on physical location

- Coherency checks between physical design information and gate-level or RTL design information

- Custom checks easy to add

- Floorplan visualization (DEF)

- User-friendly and fast GUI

- Wire length reporting

- Large customization capabilities

This email address is being protected from spambots. You need JavaScript enabled to view it.

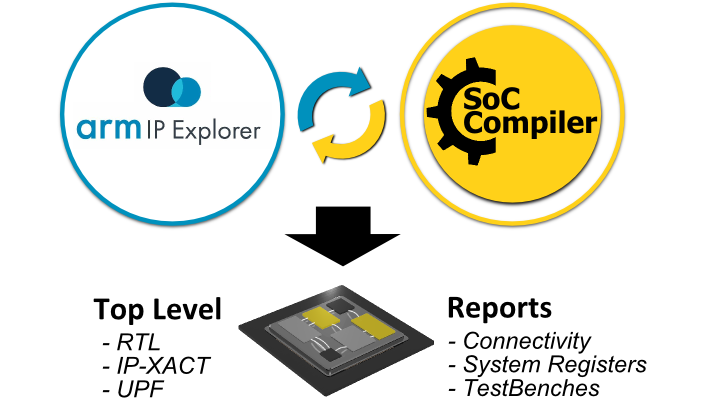

Joint Arm-Defacto SoC Design Exploration and Integration

Overview

The joint Arm IP Explorer/SoC Compiler solution is the shortest path from the definition of Arm-based system architecture to implementation and design verification. From Arm-based system architecture definition, the joint solution automatically generates top level RTL, IP-XACT, and UPF, ready for logic synthesis. This helps guide design architects to move quickly from a system definition view to a complete system ready for implementation.

Key Features

- Build graphically Arm-based subsystem using Arm IP Explorer

- Simple IP configuration

- Benefit from on-the-fly checks

- Export automatically the SoC spec into Defacto's SoC Compiler

- Generate automatically top level RTL, IP-XACT, UPF files

- Including IP and connectivity

- Benefit from Defacto's SoC Compiler reporting capabilities

- Detailed connectivity density, chip size, and power consumption

This email address is being protected from spambots. You need JavaScript enabled to view it.

For More Information :

Contact us or Access to Videos and Datasheets

Other products and solutions :

Front-End SoC Integration

Front-End SoC Integration Checks and Verifications

Checks and Verifications Open APIs and Customization

Open APIs and Customization