Considering the possibility of several segments within a single market, for example desktop, laptop, tablet, and even smartphone in computing market, imagine how many variations of an SoC or IP within it may be required. A desktop processor can be less power efficient than a tablet or smartphone processor, but needs to be highly efficient in performance.

The IP selection and integration can be more complex than we can perceive. Now a day, among a suite of standard IP blocks for particular functionalities, there can be further customization in each IP to match a particular operating environment, thus introducing differentiation in an IP. Also, IP development environments can vary with different vendors.

It’s evident that these design requirements for SoCs and IP in modern context necessitate design platforms to be versatile enough to support development and integration in multiple environments. The design platforms must be supported with multiple language APIs for development of custom applications. It’s impressive to see this innovative design framework coming up to satisfy such critical requirements for the chip design industry; designers are no longer stuck with one proprietary or standard/popular language.

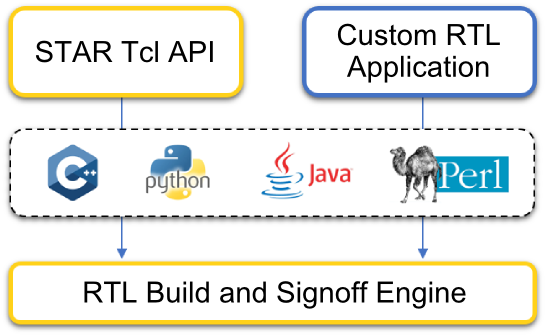

Defacto Technologies’ STAR platform provides a unique multi-language API development environment that offers the user to choose a language best suited for a particular task. While scripting languages such as Tcl, Perl, or Ruby are well-suited for tool integration, traditional programming languages along with complex data-structures and algorithms are used for application development, performance enhancement, and optimization of resources. The STAR platform is fully equipped for development of new applications as well as integration with existing tools and flows.

The STAR platform provides a differentiated solution for custom design automation that can be used for development of stand-alone applications as well as plug-ins. The key salient features in the STAR platform include –

- Unified (HDL format agnostic) APIs for design exploration and editing

- Extended support for SystemVerilog and VHDL data types

- Mixed language support

- Mixed gate-level and RTL support

- Handling of design hierarchy with queries and editing

- Advanced APIs for connectivity handling (bundle, slice, bit blasted views) through hierarchy

- File list support for simplified HDL input management

- Add-on libraries (Tcl, Python, Perl, Java, etc.) with sample applications

The STAR Application Development Environment in STAR platform is an extensive software framework with multiple sets of libraries including Perl, Python and Java. It is supported with language independent and persistent data-structures.

By using the STAR platform designers can create, explore, modify, and verify RTL designs within the same design flow. This is an ideal platform for fast design prototyping as well as development of complete new applications in shortest possible time.

Major semiconductor design companies across the globe built their custom tools on top of the STAR platform that enabled them to accelerate their design completions through seamless design flows from start to finish. A typical flow of tasks integrated on STAR platform by these design companies include –

- Design metrics and SoC topology extraction

- IP assembly at sub-system or top level

- Automatic design hierarchy restructuring based on physical design constraints

- Power aware driven design partitioning

- Feedthrough insertion to accommodate channel-less physical implementation

- Verification of structural connections including clock, I/O, and other connections

- With Defacto’s solution, the design houses can quickly build their customized yet versatile development and integration environment for a variety of SoCs catering to different target segments.

- Different versions of PPA optimized IPs from various heterogeneous environments can be integrated with ease on a single development platform. And design restructuring can be done automatically to keep the RTL in sync with physical implementation, thus reducing verification and debug cycles. The STAR RTL platform is sure to improve designers’ productivity and is proven through working silicon in several semiconductor companies.